TopMetal2-芯片是一款通过顶层金属直接收集电荷的低噪声高像素化的两维像素传感器,可鉴别幅度信息、位置信息以及时间信息。TopMetal2-芯片是采用Xfab 0.35um CMOS集成电路工艺流程制造,由72x72像素阵列、数字控制电路、数据读出电路以及外围偏置电路组成,每个像素的pitch size为83.2um,实现了每个像素噪声30e-,整个芯片功耗33mW。

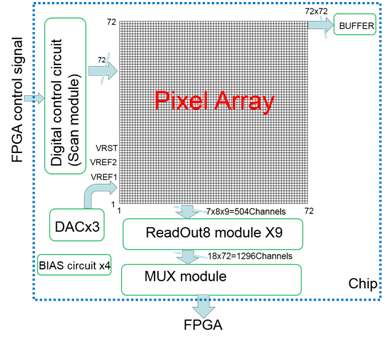

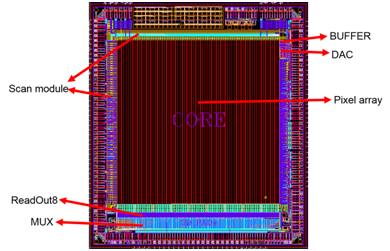

图 1 TopMetal2-整体结构

如图1所示,TopMetal2-芯片主要由pitch size为83.2um的72x72像素阵列、行列扫描控制电路(scan module)、数据读出模块、多路复用器(MUX)、3个DAC以及偏置电路组成。TopMetal2-芯片分为模拟信号读出通道和数字信号读出通道。模拟信号读出通道包含了电荷灵敏放大器(CSA)、两级源跟随(第一级输入管为p型晶体管,第二级输入管为n型晶体管)以及一个模拟BUFFER,72x72像素阵列共享该BUFFER,读取信号的幅度信息;数字信号读出通道读取时间信息和位置信息。行列扫描控制电路控制模拟读出通道,需要外部FPGA提供控制信号启动,启动后,行列扫描控制电路将从左到右,从上到下逐个像素扫描,72x72像素阵列共用一个BUFFER输出。数字读出通道每一列共用一套7bit地址总线,由优先逻辑电路仲裁哪个像素输出,像素的7bit地址信息输出给阵列下面的数据读出模块,最终由多路复用器串行输出给外部FPGA,FPGA进一步进行数据处理。每一列对应一个数据读出模块,为了方便版图布局布线,每8个数据读出模块组装成一个大模块(ReadOut8 module),72列共有9个ReadOut8 module。ReadOut8 module不仅要处理7bit地址信息,而且需要给出10bit时间信息以及1bit Ready信号,时间信息即从ReadOut8 module启动到击中像素被读出过程的计数时间,Ready信号标志该像素读出完毕,可以继续读取下一个像素。因此,ReadOut8 module输出18bit数据信息给MUX module。4个偏置电路(BIAS circuit)分别给像素内部电路提供偏置电压,72x72像素阵列共享,这样可以减小面积、功耗以及降低由偏置电路带来的mismatch。

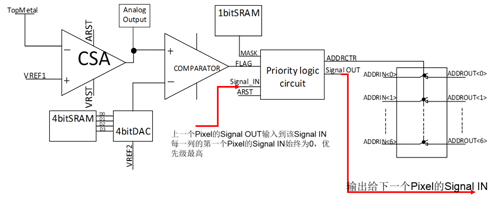

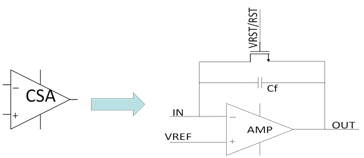

数字信号读出通道像素结构框图如图2所示,数字信号读出通道由以下部分组成:顶层金属(TopMetal)、电荷灵敏放大器(CSA)、比较器(COMPARATOR)、优先逻辑电路(Priority logic)、地址译码电路。CSA模块如图3所示,反馈电容Cf为5fF,ENC为30e-,功耗1.2uW,模拟信号读出时,复位管的栅极电压接VRST(continue reset),数字信号读出时,复位管的栅极电压接RST(active reset)。下面将详细讲述像素工作流程:a)TopMetal与CSA的负相输入端连接,CSA的正相输入端接VREF1,给CSA以及TopMetal提供合适的直流工作点(典型值600mV);b) TopMetal裸露在空气等其他环境中,电子漂移到TopMetal极板,TopMetal极板电位快速下降,经过CSA放大,CSA输出尖峰信号,peaking time为3us;c) CSA输出信号进入比较器,若信号超过比较器阈值,使得比较器翻转,判为该像素被击中。4bit SRAM与4bit DAC结合调节CSA以及COMPARATOR带来的offset,减小mismatch;d)优先逻辑电路分别有MASK、FLAG、Signal IN、ARST 4个输入信号和ADDRCTR与Signal OUT 2个输出信号。MASK作为屏蔽位,屏蔽坏像素,Signal IN与SignalOUT依次和同列相邻像素的SignalOUT与Signal IN相接,构成一串链路,共有72条链路。当FLAG为高电平,且Signal IN为低电平时,该像素将被读出,数据读出同时由ReadOut8模块给出ARST信号,复位该像素。每一列的第一个像素的Signal IN始终接低电平0,使得它在该列

图 2 单个像素结构框图

图 3 CSA模块

中优先级最高。e)优先逻辑电路输出信号ADDRCTR信号控制地址译码电路,每个像素有7bit地址,同列的不同像素地址不同,不同列的相同行的像素地址相同,一列共享一套地址总线。

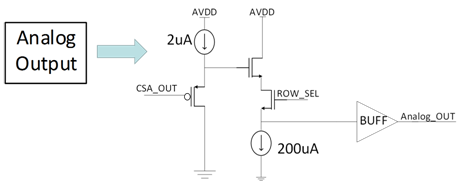

模拟信号读出通道由TopMetal、CSA、两级源跟随、模拟BUFF组成。下面介绍两级源跟随结构:第一级源跟随为p型晶体管输入管,尾电流2uA,一直处于开启状态;第二级源跟随为n型晶体管输入管,尾电流为200uA,只有在选中该像素时才会开启第二级源跟随,这样可以节省功耗。使用两级源跟随有两个目的:第一个目的是第一级源跟随一直处于开启状态,减小行选择信号耦合到CSA的输出端,甚至耦合到CSA的输入端,导致信号振荡;第二个目的是p型晶体管作为输入管可以提高直流工作点,n型晶体管作为输入管可以降低直流工作点,n型和p型互补,提高输出摆幅。

图 4 模拟信号读出通道

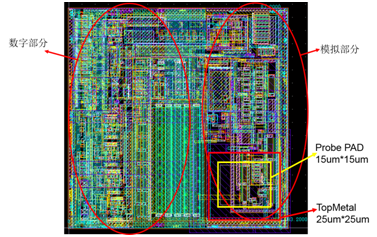

图 5 单个像素版图

单个像素版图如图5所示,布局分为数字电路部分和模拟电路部分,并且在敏感信号地方(CSA的输入端和输出端)添加屏蔽线,尽可能的减小数字电路对模拟电路造成的干扰。电源线布成网状,并有足够的宽度,尽可能的减小因电源线寄生电阻带来的电压降。单个像素的pitch size为83.2um,顶层金属面积为25x25um2,开窗面积为15x15um2。

TopMetal2-芯片整体版图布局如下:行列扫描控制电路(scan module)放置在芯片的左边和上方,方便与像素阵列连线;ReadOut8和MUX放置在芯片的底部;中间部分为像素阵列。

图 6 TopMetal2- 芯片的整体版图

目前该芯片的功能测试已经完成,芯片能够正常工作,各项指标均达到设计值。